TSMC thiết kế base die riêng cho chip nhớ HBM4, chuẩn bị ‘độc bá’ mảng AI?

Tuy không phải là công ty sản xuất chip nhớ, song phần lớn các sản phẩm sử dụng chip HBM hiện nay đều phải “qua tay” TSMC. Vì đây là nơi chúng được ghép nối với các chip xử lý khác của AMD, NVIDIA, Intel dựa trên công nghệ CoWoS. Với thế hệ HBM4, yêu cầu cần có một base (controller) die là cấp thiết để đạt hiệu năng mong muốn. Và có lẽ như công ty gia công bán dẫn hàng đầu thế giới không muốn bỏ qua cái bánh béo bở này.

Về mặt kỹ thuật, base die là một thành phần tuỳ chọn trên các thế hệ chip HBM cũ. Nhưng khi yêu cầu về băng thông ngày càng tăng lên, và trên thực tế, việc làm sao để thế hệ chip nhớ sau tốt hơn thế hệ trước ngày càng khó khăn hơn. Trước đây, Samsung, SK Hynix và Micron đều tự phát triển các sản phẩm HBM của riêng mình. Nhưng vì cùng là đối thủ, có thể nói việc hợp tác phát triển chung giữa các công ty này không đơn giản. TSMC, thì lại không phải là đối thủ (ít nhất từ góc nhìn của SK Hynix hoặc Micron).

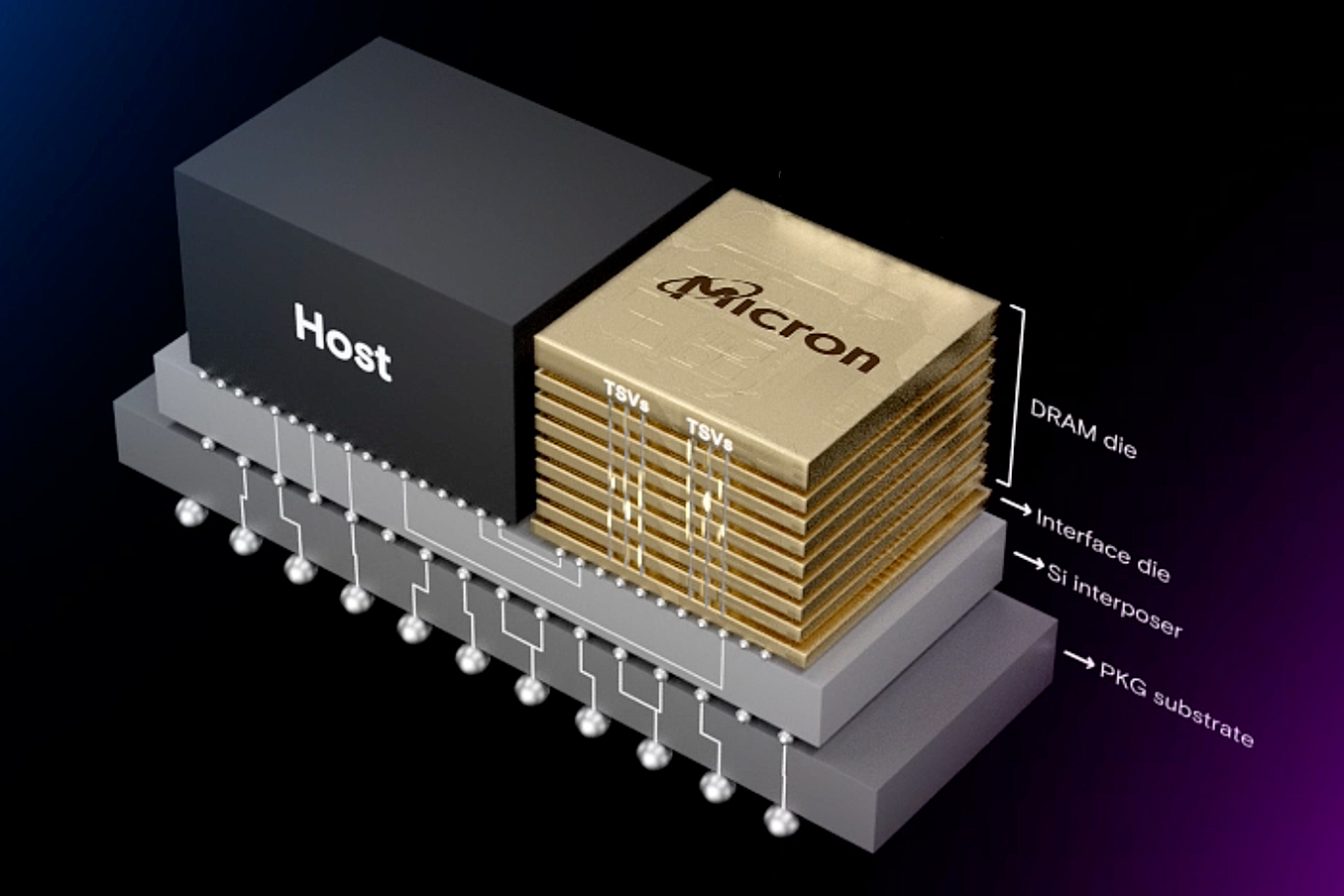

Base die hay controller hay interface die là thành phần nằm giữa stack DRAM và interposer

Base die hay controller hay interface die là thành phần nằm giữa stack DRAM và interposer

Cách đây không lâu, SK hynix cho biết sẽ hợp tác với TSMC phát triển base die mới cho HBM4. Còn tại sự kiện Symposium 2024, có vẻ base die này sẽ hoàn toàn do TSMC sản xuất, dựa trên 2 tiến trình 12 nm (N12FFC+) và 5 nm (N5). Điều này có nghĩa SK hynix chỉ cần tập trung vào việc sản xuất ra các stack HBM4. Còn làm sao để các stack HBM4 này “nói chuyện” được với các mạch logic sẽ là vấn đề của TSMC. “Chia đôi gánh nặng” như thế sẽ giúp việc phát triển trở nên nhanh và dễ dàng hơn.

Song vấn đề không chỉ nằm ở riêng SK Hynix. Như bạn có thể đã biết, hầu hết các sản phẩm ứng dụng HBM hiện nay đều là các chip tăng tốc AI. Và hầu như toàn bộ chúng đều được sản xuất ở TSMC. Như vậy bất kể là HBM của SK Hynix hay Samsung hay Micron, sau cùng đều được xuất tới TSMC. Vậy tự phát triển base die độc quyền (vốn sẽ tốn kém thời gian hơn) hay dùng của TSMC và chỉ việc lo sản xuất cho đủ sản lượng, sẽ là bài toán mà Micron lẫn Samsung phải suy nghĩ. Đặc biệt, đau đầu nhất sẽ là Samsung.

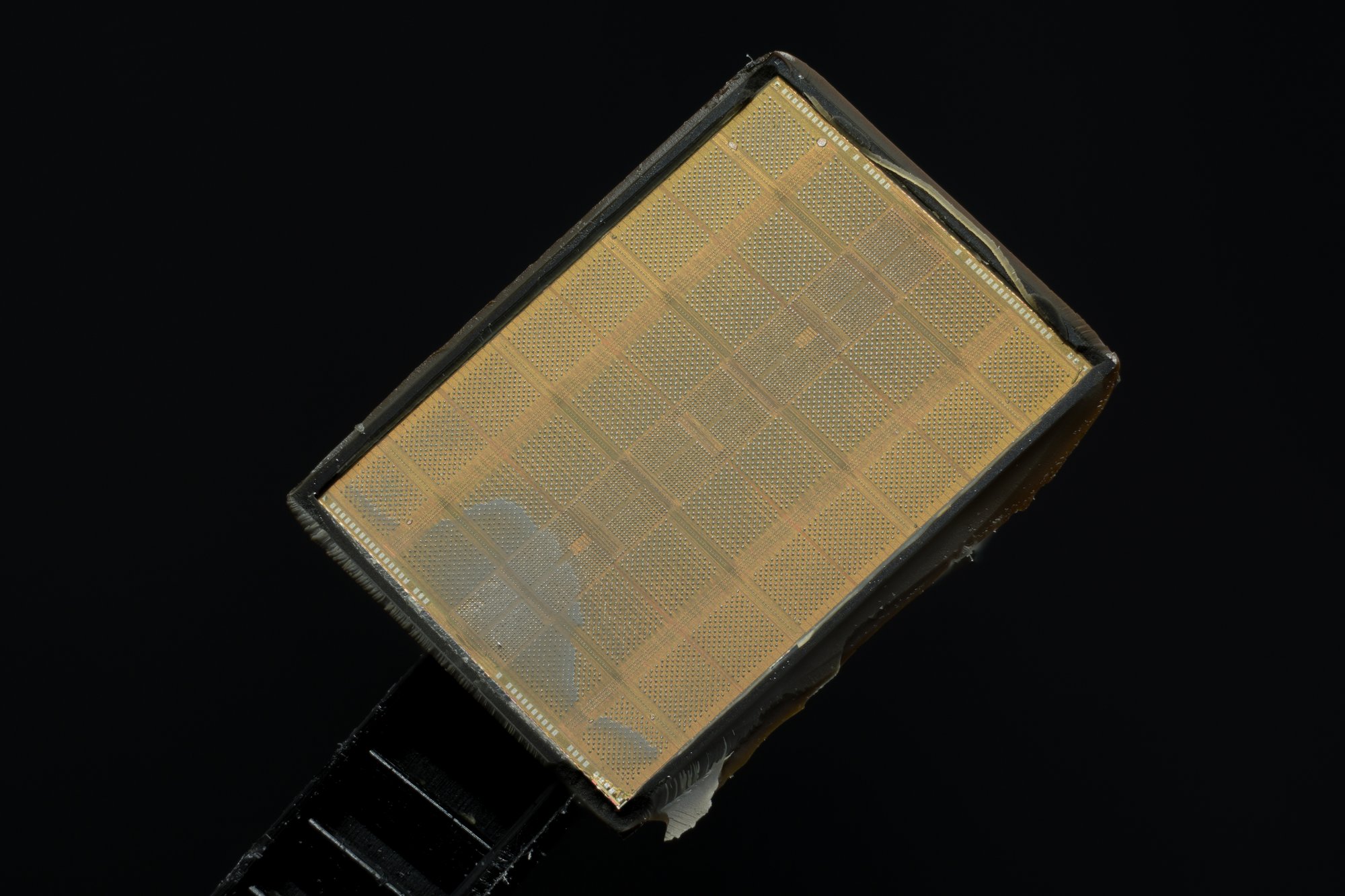

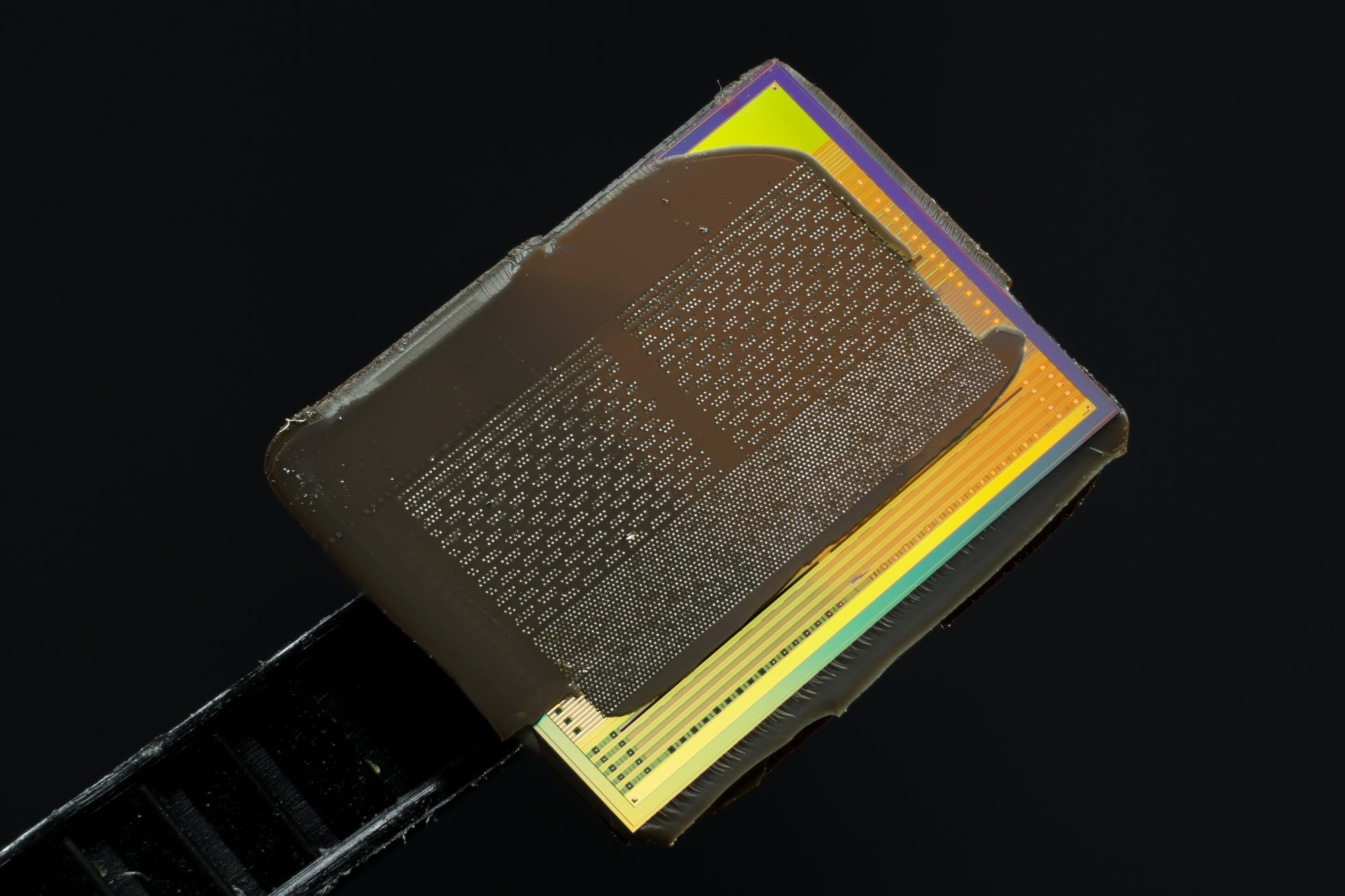

Chip base die (trên) và chip DRAM HBM (dưới)

Quay lại TSMC, công ty này sẽ có 2 giải pháp base die tuỳ theo nhu cầu của khách hàng. Về cơ bản theo TSMC, công nghệ 12 nm là đủ để đạt băng thông 2 TB/s, áp dụng cho các stack 48 GB (12-Hi) hay 64 GB (16-Hi). Công ty này cũng tối ưu lại 2 công nghệ CoWoS-L và CoWoS-R cho HBM4, với trên 8 lớp mạch điện trong đó có hơn 2000 mạch liên kết để đảm bảo độ nguyên vẹn của tín hiệu. Hiện tại theo số liệu của TSMC, các chip HBM4 đã có thể đạt băng thông 6 GT/s với dòng điện 14 mA.

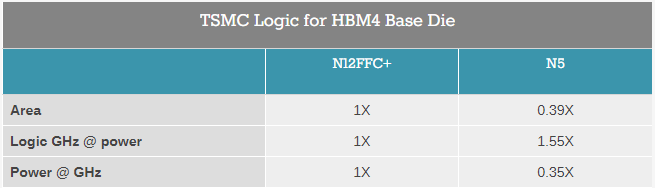

Tất nhiên, công nghệ 5 nm sẽ còn tốt hơn nhiều nữa. Nó cho phép mật độ mạch logic tăng nhiều hơn, tần số cao hơn (ở cùng điện áp) hoặc tiết kiệm điện hơn (ở cùng tần số). Nhưng quan trọng hơn là base die 5 nm có bề rộng các mạch liên kết rất nhỏ, từ 6 – 9 micron. Đặc điểm này cho phép hãng thiết kế chip đặt trực tiếp (direct bonding) base die lên die chip chính (stack HBM4 sẽ nằm trên base die), giúp đạt hiệu năng cao hơn so với phương pháp đặt liền kề như hiện nay.

So sánh base die HBM4 12 nm vs. 5 nm của TSMC

Nhìn chung, nếu base die của TSMC thực sự “ngon”, thì có thể thấy tương lai mảng AI đều do một tay che trời…