Phân tích kiến trúc AMD Zen 5 – Cải tiến lớn nhất kể từ Zen ‘đời đầu’ (phần 1)

Năm nay quả thật là một năm đầy sự kiện trong thị trường vi xử lý toàn cầu, khi các đại gia đều lần lượt tung ra những quân bài chủ lực vốn được “nung nấu” trong nhiều năm trời trước khi tung lên chợ. Ai sẽ người chiến thắng chung cuộc trong vòng đua 2024? Hãy còn sớm để trả lời. Lần trước mình đã phân tích cơ bản về kiến trúc Lion Cove (thuộc Lunar Lake & Arrow Lake) của Intel, hôm nay chúng ta sẽ điểm qua chi tiết hơn Zen 5 – mà trong quan điểm của mình, là cuộc cách mạng lớn nhất của AMD kể từ thế hệ Zen đầu tiên ra mắt 7 năm trước.

Một chút chuyện xưa

Bạn có thể nghĩ Zen 5 thì có gì “đao to búa lớn”, nó chẳng phải là kiến trúc mới hơn Zen 4 sao? Đúng là như vậy, nhưng Zen 5 không chỉ mới hơn Zen 4, mà nó còn mới hơn cả Zen 1/2/3, vốn là “xương sống” của AMD suốt 7 năm qua. Và cả 4 thế hệ Zen đầu tiên nay đã “có tuổi”, chúng đã cứu AMD thoát khỏi vũng lầy phá sản. Dù vậy với sự biến động và cạnh tranh liên tục của thị trường công nghệ, không kiến trúc nào có thể “an toàn” mãi mãi – Zen 5 sẽ là sự khởi đầu mới cho AMD, cũng như Zen 1 đã lột xác công ty từ kiến trúc Bulldozer mang nhiều tai tiếng.

Nhắc lại “chuyện cái ao”, Bulldozer là kiến trúc AMD đã đặt rất nhiều tâm huyết vào để phát triển, so với kiến trúc K7 trước đó. Tuy vậy nhiều năm trời chạy đua với Intel nhất là về dây chuyền bán dẫn, đã khiến AMD bị “đuối hơi” thấy rõ. Trong giai đoạn 2010, AMD thường xuyên thua lỗ, dẫn tới quá trình thiết kế Bulldozer bị dang dở. Sau cùng công ty này chọn sử dụng các công cụ thiết kế tự động (thay vì kỹ sư chỉnh tay) can thiệp vào rất nhiều phần của con chip. Kết quả là dù thiết kế ban đầu chỉ cần 1.2 tỷ transistor nhưng sau cùng lại vọt tới 2 tỷ!

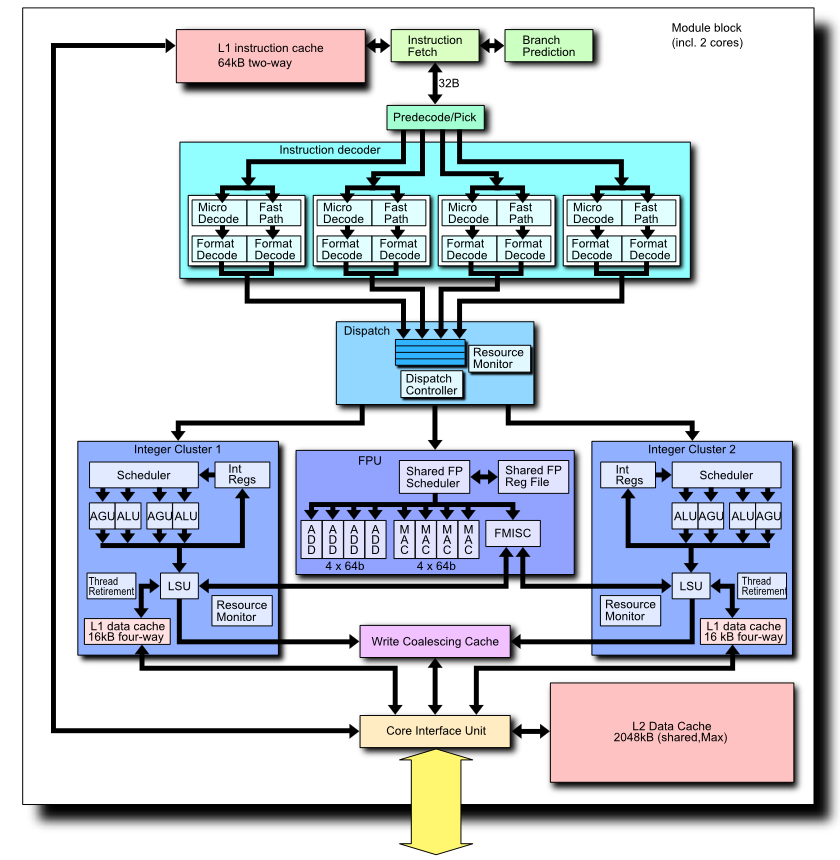

Sơ đồ khối kiến trúc Bulldozer với 2 cụm INT và 1 FPU

Ngoài vấn đề “lạm phát” transistor, Bulldozer còn mang theo một nhược điểm không thể khắc phục là “tầm nhìn” nhân xử lý của AMD lúc bấy giờ. Thay vì thiết kế 1 nhân INT (số nguyên) “bự” giống Intel, các kỹ sư AMD chọn cách “chẻ đôi” thành 2 nhân INT “nhỏ” và đi kèm 1 nhân FPU. Đường lối CMT (Clustered Multi Threading) tuy hay hơn SMT (Simultaneous Multithreading hay Hyper Threading) vì tạo ra nhiều nhân “thực” thay vì xài nhân “ảo”, song điểm dở là những nhân “thực” này lại “còi xương” quá đỗi. Trên thực tế 1 nhân INT K10 có tới 3 ống lệnh để xử lý thì 1 nhân INT Bulldozer chỉ có 2 ống lệnh! Kết quả là con chip 8 nhân “còi xương” Bulldozer đôi khi chạy thua cả con chip 6 nhân K10…

Dù vậy, nhiều chuyên gia IT cho rằng “đếm” nhân xử lý là “đếm” số lượng FPU, không phải INT. Và họ cho rằng con chip Bulldozer đúng ra chỉ có 4 nhân (vẫn xử lý được 8 luồng). Nếu marketing theo cách này thì Bulldozer không quá tệ. Nhưng mà lãnh đạo AMD lúc đó tương đối… bảo thủ và cái giá của bảo thủ thường là bị knock-out.

Các bản nâng cấp của Bulldozer trở về sau, gồm Piledriver, Steamroller, Exacavator (lúc này Lisa Su đã cầm lái AMD) tuy có tốt hơn thế hệ đầu, nhưng vì vẫn dựa trên triết lý nhân “còi” nên gần như chỉ nằm “chiếu dưới” so với dòng Core nhà Intel. Thay đổi “xương sống” là điều sống còn với công ty này.

Zen “đời đầu” – Trở lại big core

Như bạn đã thấy ở trên, sai ngay từ cái gốc rất là tai hại. Vì dư âm nó để lại sẽ kéo dài qua nhiều năm tháng, ảnh hưởng tới cả sự tồn vong của một doanh nghiệp. Có thể nói những năm đầu tiên cầm trịch ở AMD là những năm Lisa Su lo dọn dẹp đống bầy nhầy mà các đời CEO trước (Dirk Meyer, Rory Read) bỏ lại. Đây cũng là giai đoạn AMD bán chip game console “cầm hơi qua ngày”. Tất cả vì canh bạc Zen theo đúng nghĩa “được ăn cả, ngã ra đê nằm”.

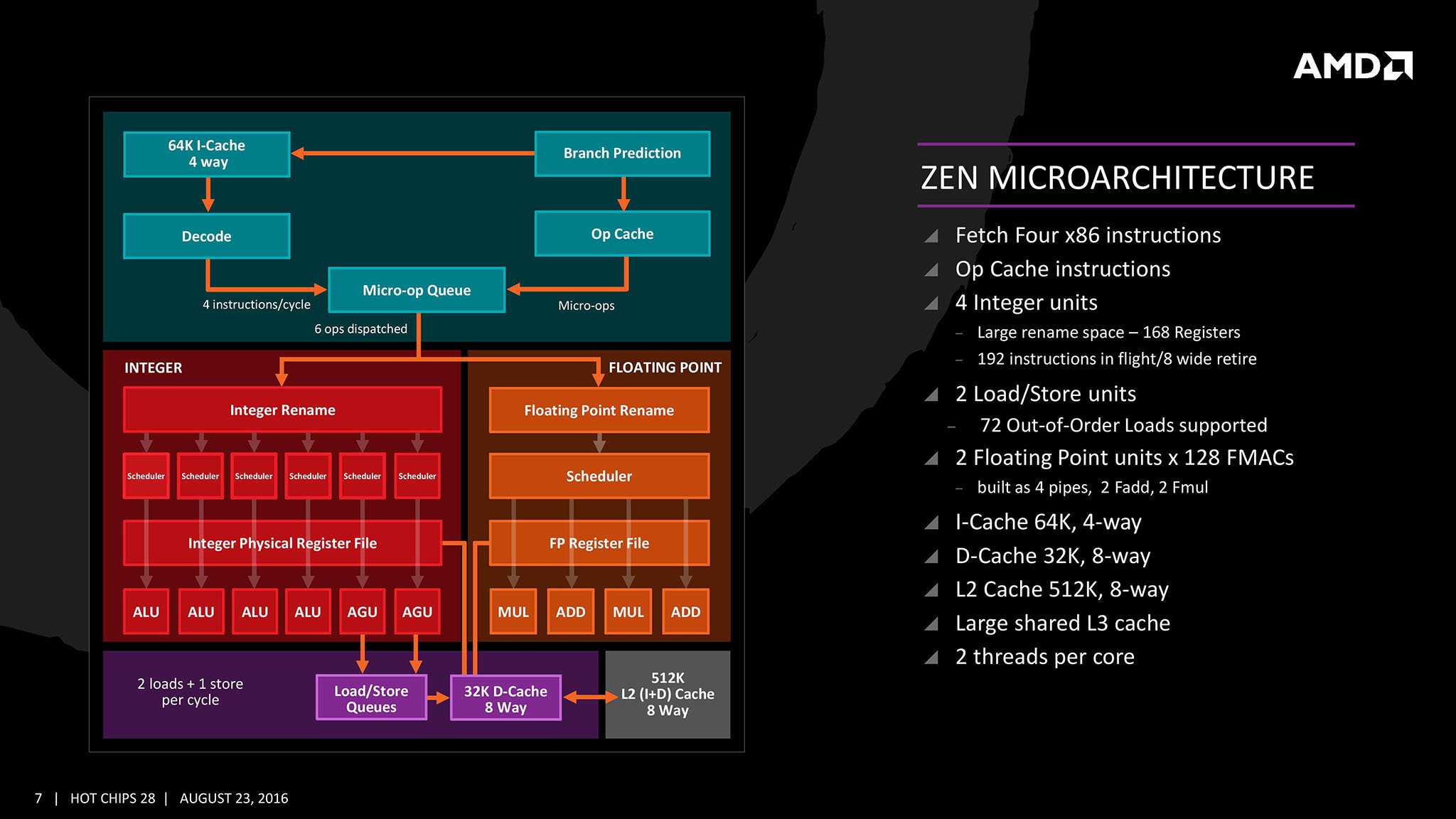

Kiến trúc Zen được công bố vào 2016 và ra mắt sản phẩm trong 2017

Công tâm mà nói, kiến trúc Zen gần tương tự với Skylake bên Intel, nhưng đơn giản hơn một chút. Và tại thời điểm 2017, tâm lý chung lúc đấy là liệu AMD có thể còn làm được chip x86 hay không, chứ không phải là có thể làm được sản phẩm tốt hơn Intel. Ngoài việc Zen từ bỏ con đường CMT của Bulldozer (mà đi theo con đường SMT như Intel), thì quân bài khác mà Lisa Su có trong tay chính là chiplet!

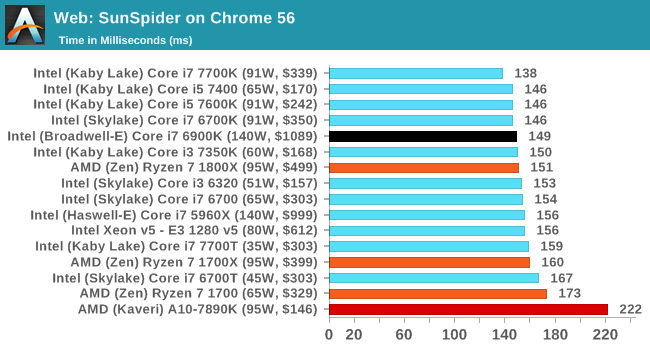

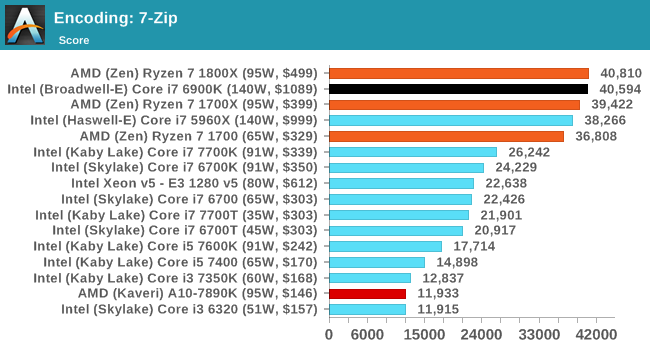

Bản thân hiệu năng đơn luồng của Zen vẫn thấp hơn Skylake, song với triết lý số lượng cũng là một dạng chất lượng, con chip 8 nhân Zen (không phải 8 nhân “còi xương” Bulldozer) dễ dàng đè bẹp Core i7-7700K (4 nhân) của Intel. Và từ đó, các thế hệ Zen trở về sau là bản nâng cấp dần lên từ Zen “đời đầu”. Nếu so sánh, bạn sẽ thấy Zen 4 về cơ bản không khác biệt nhiều lắm Zen 1, trừ việc vị trí nào cần được thêm thì thêm, thừa thì bớt. Nhưng khác biệt chính với Bulldozer là Zen dùng nhân INT “xịn”, chứ không phải chẻ đôi như trước.

Dĩ nhiên cũng cần nói thêm sự trở lại của AMD ngoài địa lợi, nhân hoà ra còn có thêm thiên thời từ Intel. Như mình đã kể ở trước, giai đoạn Zen ra mắt thị trường cũng là lúc Intel bắt đầu bất ổn với dàn CEO nay người này mai người kia. Trong khi AMD liên tục nâng cấp công nghệ bán dẫn (nhờ thuê TSMC) thì Intel vẫn “gà cồ ăn quẩn cối xoay” 14+++ nm. Việc Intel dậm chân tại chỗ vô tình giúp AMD có thêm điều kiện để rút ngắn khoảng cách rồi vượt mặt huy hoàng như hôm nay.

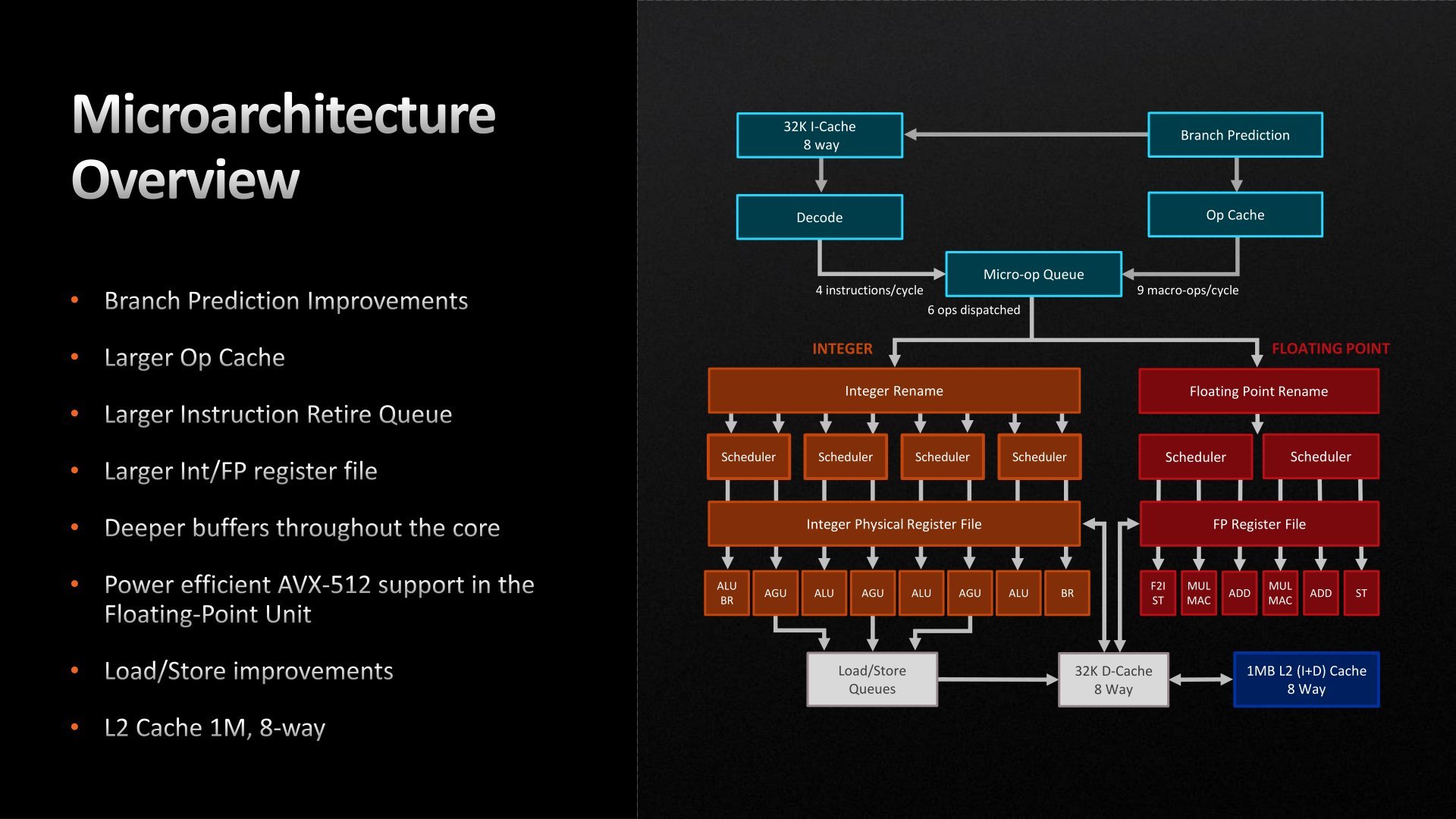

Kiến trúc Zen 4 sau 7 năm cải tiến

Nhưng công nghệ là một thị trường khắc nghiệt, nếu AMD cũng ngủ quên trên chiến thắng như đối thủ, thì lịch sử sẽ lặp lại…

Những thử thách mới

Thực tế mà nói, để “thai nghén” một kiến trúc mới hoàn toàn là công việc không phải sớm muộn. Hầu hết các công ty như AMD hay Intel đều có ít nhất 2 nhóm kỹ sư chuyên biệt để thiết kế chip theo kiểu luân phiên, hoặc 1 nhóm chuyên làm kiến trúc lớn (lộ trình trung bình 5 năm) và 1 nhóm chuyên nâng cấp lên từ đó (nói như kiểu lập trình là mỗi năm lại nâng cấp, sửa lỗi thêm vài tính năng). Tương tự để làm ra Zen 1 (ra 2016) thì Lisa Su phải lên kế hoạch ngay từ lúc vừa về AMD (2012). Và để ra Zen 5 thì nó cũng phải được tính toán muộn nhất từ 2020.

Dàn lãnh đạo AMD khi bắt đầu giới thiệu về Zen

Có nghĩa Zen 5 sẽ như thế nào là phải “được thấy” từ nhiều năm trước, chứ không phải tới khi Qualcomm tung ra Snapdragon X hay Intel ra Lunar Lake, Arrow Lake… thì AMD mới cuống lên chạy. Điều này đòi hỏi năng lực về tầm nhìn của lãnh đạo hết sức quan trọng (thực tế như tầm nhìn Bulldozer hồi 2010 đã để lại quả đắng nghét cho chính công ty này). Đến khi kiến trúc Zen 5 được chính thức công bố, mình có thể nói – đấy là một tầm nhìn rất đúng đắn!

Còn nhớ ở bài phân tích Lunar Lake mà nổi bật là nhân Lion Cove, mình từng đề cập tới việc không riêng AMD mà Intel cũng đang gặp áp lực lớn từ phe Arm, đặc biệt từ Apple và Qualcomm. Các sản phẩm bên RISC đã …….. 8/10-wide decoder trong khi phe x86 chỉ mới là 4/6-wide. Tuy kích thước decoder không nói lên kiến trúc A mạnh hơn B C D hay ngược lại nhưng ít nhất nó thể hiện mức IPC (tối đa) mà kiến trúc đó có thể đạt. Nếu AMD hay Intel không tăng kích thước decoder lên cho ít nhất là ngang ngửa với Arm thì thực khó để có thể cạnh tranh lại. Với Intel, công ty này đã tăng dần từ 4-wide (Skylake) lên 5-wide (Cypress Cove) rồi 6-wide (Redwood Cove) và mới nhất là 8-wide (Lion Cove).

Zen không tốt hơn Skylake ở đơn luồng nhưng lại vượt trội ở đa luồng nhờ có nhiều nhân xử lý

Còn AMD? Suốt 7 năm qua công ty này vẫn “giậm chân tại chỗ” ở 4-wide (Zen 1, 2, 3, 4). Thực tế Bulldozer cũng là 4-wide decoder nhưng do đặc trưng “chẻ đôi” INT nên không hẳn là 4-wide đúng nghĩa. Nhưng chính vì thế mà mình từng “ngại” rằng AMD sẽ bị “đuối” vì việc tăng decoder không phải là chuyện dễ dàng với CISC. Kể cả lên 6-wide vào lúc này cũng là một điều không dễ dàng cho AMD (hãy nhìn Intel đã tăng từ từ như thế nào).

Ấy thế mà…

Zen 5 chơi tới 8-wide. Giỡn mặt à?

Bài cũ, rượu không cũ

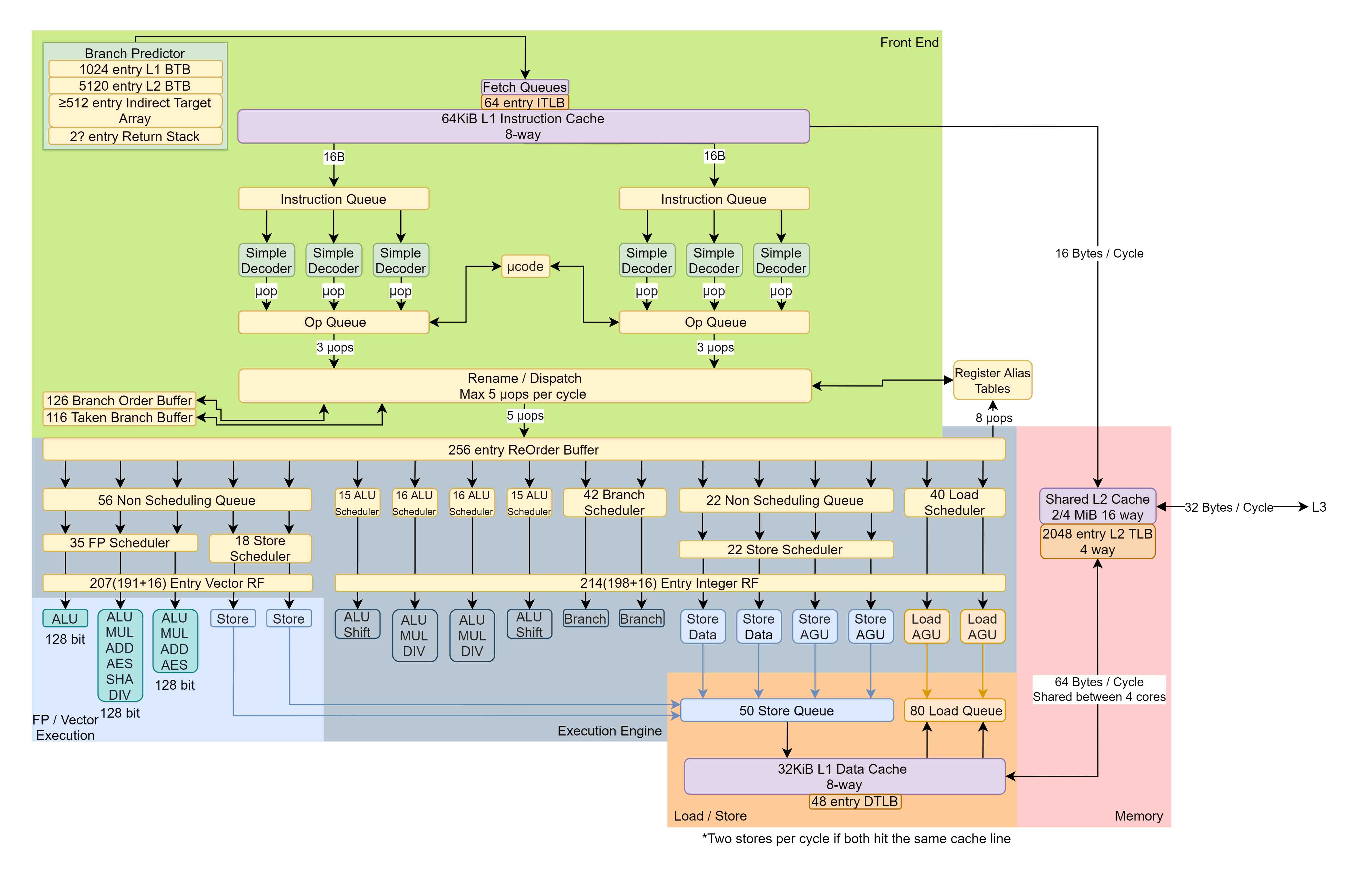

Thực sự khi theo dõi sự kiện của AMD tại Computex, mình vừa ngạc nhiên lại hết sức bất ngờ trước cái cách công ty này “cheat” decoder. Nó vừa gợi nhớ lại Bulldozer của chính công ty này, cũng gợi nhớ tiếp tới E-Core Gracemont nhà Intel. Nhưng điều đáng nói là Intel dùng E-core với ý nghĩa tiết kiệm điện, trong khi AMD dùng Zen 5 hoàn toàn như một P-core “real”. Cụ thể là thay vì dùng 1 decoder 8-wide to bự hoành tráng và phức tạp, tại sao không “chẻ đôi” thành 2 decoder 4-wide?

Tất nhiên nếu là fan Intel, bạn có thể nói AMD đã copy chiêu này từ E-core, nhưng mình cho rằng ý tưởng này được thừa kế lại từ Bulldozer. Vì công ty này có không ít lần làm giới công nghệ ngạc nhiên với những giải pháp đơn giản mà hiệu quả không kém gì đối thủ. Ví như bộ mở rộng AMD64 cho phép kiến trúc x86 hỗ trợ xử lý 64-bit mà không cần phải “đập bỏ toàn bộ” kiến trúc cũ như IA64 phía Intel. Kết quả là con tàu Itanium “chìm” không sủi tăm trước sự đơn giản tới ngỡ ngàng của x86-64 (tên gọi khác của AMD64).

Và lần này, là bộ decoder 4-wide đôi!

E-core Gracemont của Intel cũng sử dụng 2 decoder độc lập

Tất nhiên, ở đây mình không khẳng định là cách làm của Intel (và Apple, Qualcomm) tốt hơn hay AMD tốt hơn. Nó cũng gần giống việc so sánh cục máy 300 cc chỉ có 1 piston (bự) thì hơn hay thua 2 piston (nhỏ). Hiệu quả thực tế sẽ còn lệ thuộc vào những thành phần khác. Vả chăng, tuy cùng là 4-wide decoder nhưng hệ số IPC giữa Zen 1, 2, 3 và 4 là rất khác biệt. Tương tự Zen 6, 7… có thể vẫn cùng decoder như Zen 5 nhưng hiệu quả cũng sẽ khác.